# **Deliverable D5.1**

# **WP5 First Intermediate Report**

# **Cross Cutting Issues Working Groups**

| CONTRACT NO | EESI2 312478                           |

|-------------|----------------------------------------|

| INSTRUMENT  | CSA (Support and Collaborative Action) |

| THEMATIC    | INFRASTRUCTURE                         |

Due date of deliverable: <31 July 2013> Actual submission date: <19 July 2013> Publication date:

Start date of project: 1 September 2012

Duration: 30 months

Name of lead contractor for this deliverable: Giovanni Erbacci, CINECA

Authors: Giovanni Erbacci (CINECA), Francois Bodin (CAPS), Vincent Bergeaud (CEA), Alberto Pasanisi (EDF), Simon McIntosh-Smith (Bristol Univerity), Thomas Ludwig (DKRZ), Franck Cappello (INRIA), Carlo Cavazzoni (CINECA), Marie-Christine Sawley (Intel).

Name of reviewers for this deliverable:

Abstract: First intermediate report on cross cutting issues, presenting the outcome of the first year of activity of the five working groups identified in EESI-2 WP5.

Revision 1.0

| Project co-funded by the European Commission within the Seventh Framework Programme (FP7/2007-2013) |                                                                                                  |   |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---|

| Dissemination Level                                                                                 |                                                                                                  |   |

| PU                                                                                                  | Public                                                                                           |   |

| PP                                                                                                  | PP Restricted to other programme participants (including the Commission Services)                |   |

| RE                                                                                                  | RE         Restricted to a group specified by the consortium (including the Commission Services) |   |

| со                                                                                                  | Confidential, only for members of the consortium (including the Commission Services)             | Х |

# **Table of Contents**

| 1.                                      | EXE                                                                                                                                                    | ECUTIVE SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                               |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 2.                                      | LIS                                                                                                                                                    | T OF EXPERTS AND WORK METHODOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .10                                                                                                             |

|                                         | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                                                                                        | WG 5.1 DATA MANAGEMENT AND EXPLORATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11<br>12<br>12                                                                                                  |

| 3.                                      | WG                                                                                                                                                     | 5.1 DATA MANAGEMENT AND EXPLORATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .14                                                                                                             |

|                                         | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                                                                        | INTRODUCTION<br>CHALLENGES<br>IMPACT ON APPLICATION DEVELOPMENT<br>FINDINGS<br>RECOMMENDATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15<br>15<br>16                                                                                                  |

| 4.                                      | WG                                                                                                                                                     | 5.2 UNCERTAINTIES (UQ / V&V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .18                                                                                                             |

| 2                                       | 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5.                                                                                                  | DOE-BASED UNCERTAINTY ANALYSIS METHODS.         1       Methodologies.         2       Tools         FIRST RECOMMANDATIONS FOR EXASCALE.         1       Diffusion of tools and practices.         2       Progresses in numerical analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19<br>19<br>20<br>20<br>22<br>24<br>24<br>24<br>24                                                              |

|                                         | 4.5.                                                                                                                                                   | 3 Specifications for future software and architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                                                                                                              |

| 5.                                      |                                                                                                                                                        | <ul> <li>Specifications for future software and architectures</li> <li>5.3 POWER &amp; PERFORMANCE</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                 |

|                                         | <b>WG</b><br>5.1<br>5.2                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .26<br>26<br>26<br>27<br>29                                                                                     |

|                                         | WG<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                                                                  | 5.3 POWER & PERFORMANCE.<br>INTRODUCTION<br>THE REMAINING KEY ENERGY EFFICIENCY AND POWER MANAGEMENT CHALLENGES TO ACHIEVE<br>CALE SYSTEMS.<br>CURRENT STATE OF THE ART<br>GAP ANALYSIS FOR EACH CHALLENGE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .26<br>26<br>27<br>29<br>31                                                                                     |

| 6. 000                                  | WG<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>WG<br>5.1<br>5.2<br>5.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6                   | 5.3 POWER & PERFORMANCE.         INTRODUCTION.         THE REMAINING KEY ENERGY EFFICIENCY AND POWER MANAGEMENT CHALLENGES TO ACHIEVE         CALE SYSTEMS.         CURRENT STATE OF THE ART         GAP ANALYSIS FOR EACH CHALLENGE.         RECOMMENDED SPECIFIC ACTIONS FROM WG5.3         5.4 RESILIENCE.         INTRODUCTION         EESI1 RECOMMENDATIONS         RELIABILITY, AVAILABILITY SERVICEABILITY SYSTEM.         1       At Node HW level         2       At Node system level         3       At interconnect level         4       At File system and storage level.         RUNTIME.         HIGH PERFORMANCE CHECKPOINTING         MULTILEVEL CHECKPOINTING         ADVANCED FAULT TOLERANT PROTOCOLS         MPI AND OTHER PROGRAMMING MODELS.                                                                                                                                                                                                                                                                                                    | .26<br>26<br>27<br>29<br>31<br>.32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>35<br>36<br>37<br>38      |

| 6. 000                                  | WG<br>5.1<br>5.2<br>EXASC<br>5.3<br>5.4<br>5.5<br>WG<br>5.1<br>5.2<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>6.3<br>5.4<br>5.5<br>5.6<br>5.7 | 5.3 POWER & PERFORMANCE.         INTRODUCTION         THE REMAINING KEY ENERGY EFFICIENCY AND POWER MANAGEMENT CHALLENGES TO ACHIEVE         CALE SYSTEMS         CURRENT STATE OF THE ART         GAP ANALYSIS FOR EACH CHALLENGE.         RECOMMENDED SPECIFIC ACTIONS FROM WG5.3         5.4 RESILIENCE         INTRODUCTION         EESI1 RECOMMENDATIONS         RELIABILITY, AVAILABILITY SERVICEABILITY SYSTEM.         1       At Node HW level         2       At Node system level         3       At interconnect level         4       At File system and storage level         RUNTIME       HIGH PERFORMANCE CHECKPOINTING         MULTILEVEL CHECKPOINTING       ADVANCED FAULT TOLERANT PROTOCOLS                                                                                                                                                                                                                                                                                                                                                       | .26<br>26<br>27<br>29<br>31<br>.32<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>36<br>37<br>38<br>38            |

| 6. 000000000000000000000000000000000000 | WG<br>5.1<br>5.2<br>EXASC<br>5.3<br>5.4<br>5.5<br>WG<br>5.1<br>5.2<br>5.3<br>6.3.<br>6.3.<br>6.3.<br>6.3.<br>6.3.<br>6.3.<br>6.3.                      | 5.3 POWER & PERFORMANCE.         INTRODUCTION.         THE REMAINING KEY ENERGY EFFICIENCY AND POWER MANAGEMENT CHALLENGES TO ACHIEVE         ALE SYSTEMS.         CURRENT STATE OF THE ART         GAP ANALYSIS FOR EACH CHALLENGE.         RECOMMENDED SPECIFIC ACTIONS FROM WG5.3         5.4 RESILIENCE.         INTRODUCTION.         EES11 RECOMMENDATIONS         RELIABILITY, AVAILABILITY SERVICEABILITY SYSTEM.         1       At Node HW level         2       At Node system level         3       At interconnect level         4       At File system and storage level.         RUNTIME.         HIGH PERFORMANCE CHECKPOINTING         MULTILEVEL CHECKPOINTING         ADVANCED FAULT TOLERANT PROTOCOLS         MPI AND OTHER PROGRAMMING MODELS.         FAILURE PREDICTION | .26<br>26<br>27<br>29<br>31<br>.32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>3 |

### D5.1 FIRST INTERMEDIATE REPORT ON CROSS CUTTING ISSUES

| 7.3   | PACKAGING              |    |

|-------|------------------------|----|

| 7.4   | DATA TRANSFER          |    |

| 7.5   | Memory                 |    |

| 7.6   | Network                |    |

| 7.7   | I/O SUBSYSTEM          |    |

| 7.8   | COOLING                |    |

| 7.9   | NEXT STEPS             |    |

| 8. Bl | BLIOGRAPHY             | 56 |

| 9. AN | NNEXES                 | 58 |

| 9.1   | LIST OF EXPERTS IN WGS |    |

|       |                        |    |

# List of Figures

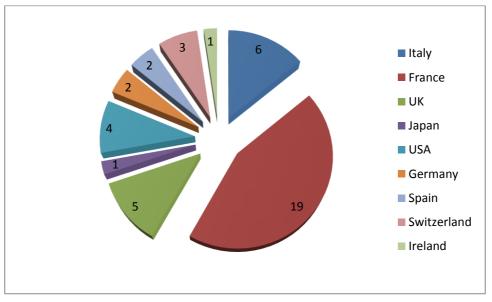

| Figure 1: WP5 Experts distributed per Country (43 Experts from 9 Countries)                           | 10   |

|-------------------------------------------------------------------------------------------------------|------|

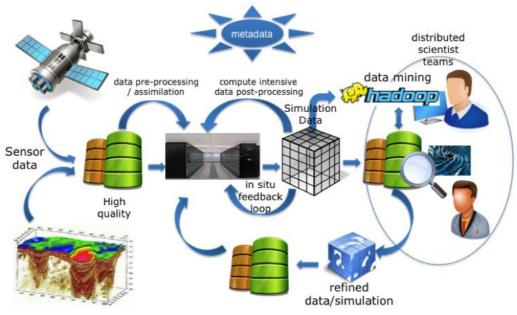

| Figure 2: Complex work flow of Exascale applications                                                  | 14   |

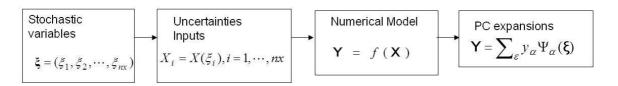

| Figure 3: Principle of spectral expansions                                                            |      |

| Figure 4: Uncertainty analysis methodology                                                            |      |

| Figure 5: Common methods for sensitivity analysis                                                     | 21   |

| Figure 6: New non volatile memory technologies                                                        |      |

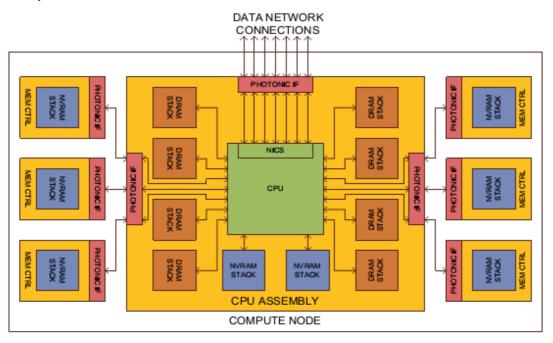

| Figure 7: Potential architecture of an Exascale computer node                                         |      |

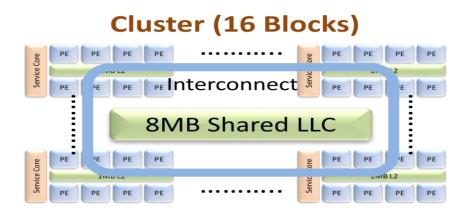

| Figure 8: Cluster of core blocks of the NTV chip (courtesy of S. Burkar)                              | 40   |

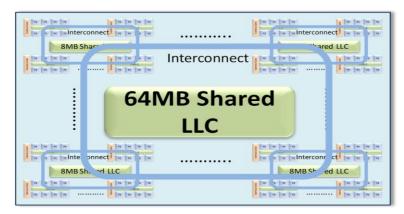

| Figure 9: Hierarchical structure of NTV chip (courtesy of S. Burkar)                                  | 41   |

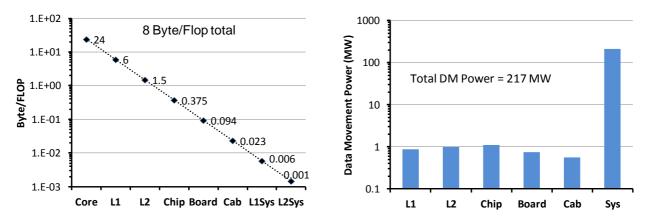

| Figure 10: Typical power dissipated by moving data across different layer of the memory hierarchy.    | 42   |

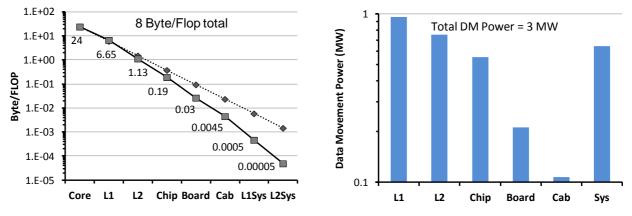

| Figure 11: Estimated power dissipated by data movement using "intelligent" tapering techniques        | 42   |

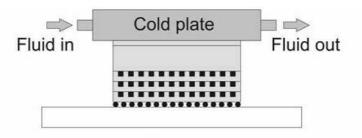

| Figure 12: Microchannel based cooling system                                                          | 44   |

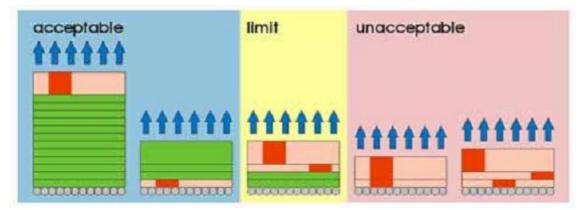

| Figure 13: Different physical layout of 3D stacking with microchannel cooling                         |      |

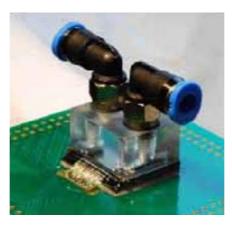

| Figure 14: Lab test sample of a microchannel cooled chip                                              | 44   |

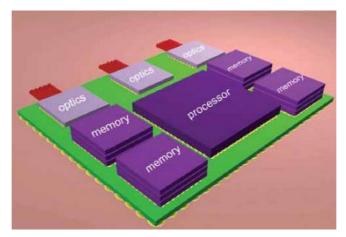

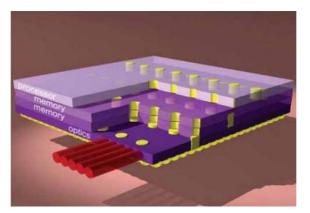

| Figure 15: Single die design with processor, optical interconnect and 3D memory                       | 45   |

| Figure 16: 3D packaging of optical interconnect, memory and processor                                 |      |

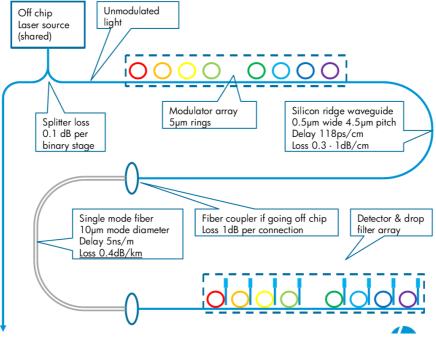

| Figure 17: Draft schema of photonic data transport circuit                                            |      |

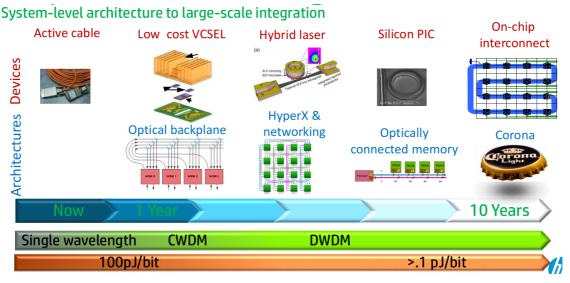

| Figure 18: Estimated roadmap of photonic technology                                                   | 47   |

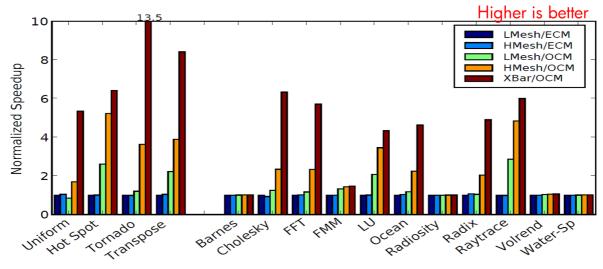

| Figure 19: Simulated performances of different numerical kernels, for different switch infrastructure | ə.48 |

| Figure 20: Optical interconnection internal to the node of an exascale system                         | 48   |

| Figure 21: Main characteristics of optical interconnect (projected for 2016 and 2020)                 | 49   |

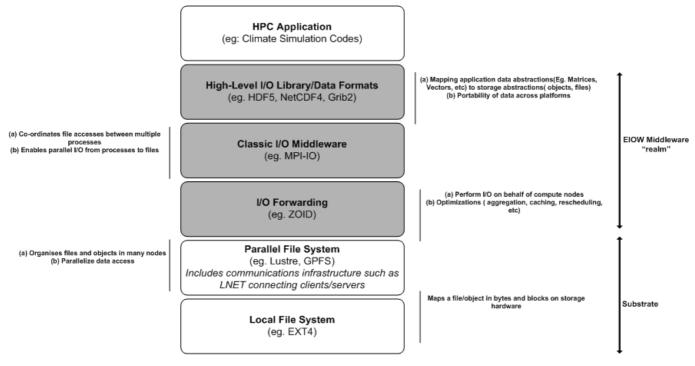

| Figure 22: I/O "middleware" stack for a typical HPC application                                       | 52   |

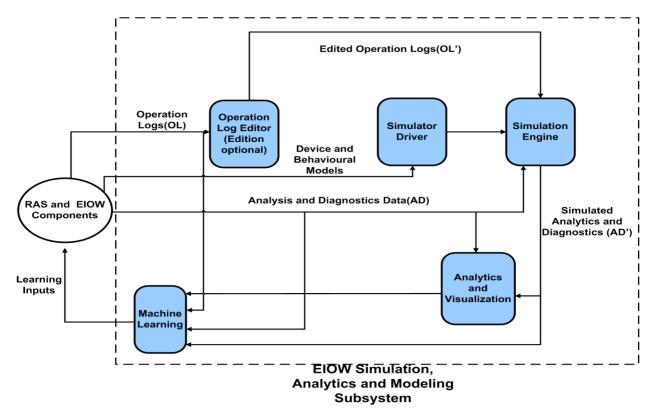

| Figure 23: System Diagnostics/Analytics/Simulation, big picture architecture                          | 53   |

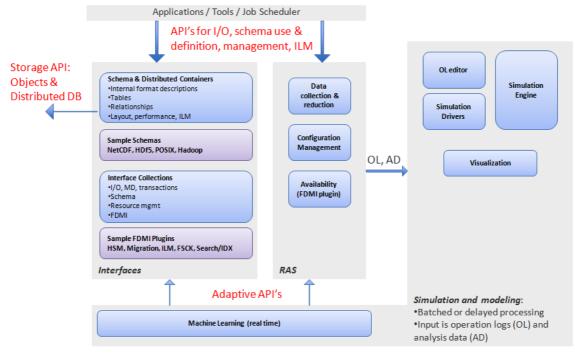

| Figure 24: EIOW High Level Architecture Summary                                                       | 54   |

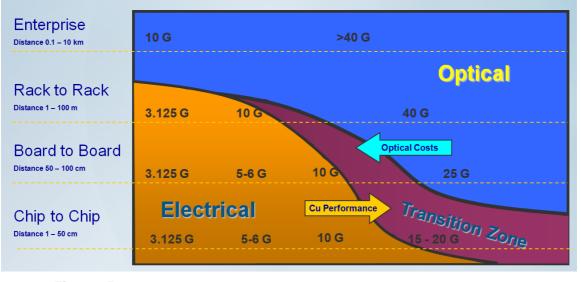

| Figure 25: Performance, distance and cost phase diagram for different physical transport media        | 54   |

# List of Tables

| Table 1: Agenda of the Workshop on HPC and Uncertainties, Paris, 22-23 April 2013 | .12 |

|-----------------------------------------------------------------------------------|-----|

| Table 2: Agenda of the Workshop on Disruptive Technoloogies, Milan, 15 April 2013 | .13 |

| Table 3: Main characteristics of NTV chips                                        | .41 |

# Glossary

| Abbreviation / acronym | Description                                                             |

|------------------------|-------------------------------------------------------------------------|

| ABFT                   | Algorithm-Based Fault Tolerance for Linear Algebra                      |

| ACPI                   | Advanced Configuration and Power Interface                              |

| ADS                    | Adaptive Directional Stratification                                     |

| ANL                    | Argonne National Lab                                                    |

| API                    | Application Programming Intreface                                       |

| ARM                    | Advanced RISC Machine                                                   |

| BMBF                   | Federal Ministry of Education and Research (Germany)                    |

| CDF                    | Cumulative Distribution Function                                        |

| CEA                    | Commissariat à l'énergie atomique et aux énergies alternatives          |

| CINECA                 | Centro di Calcolo Interuniversitario. The Italian Supercomputing Centre |

| CMOS                   | Complementary Metal-Oxide Semiconductor                                 |

| СМР                    | Chip Multiprocessor                                                     |

| CPU                    | Central Processing Unit                                                 |

| CRESTA                 | Collaborative Research into Exascale Systemware Tools&Applications      |

| DAKOTA                 | Design Analysis Kit for Optimization and Terascale Applications         |

| DARPA                  | Defense Advanced Research Projects Agency                               |

| DDDC                   | Double Device Data Correction                                           |

| DDDC+1                 | memory enhanced Double Device Data Correction                           |

| DDR                    | Double Data Rate                                                        |

| DEEP                   | Dynamical Exascale Entry Platform. EU funded Exascale FP7 Project       |

| DIMM                   | Dual In-line Memory Module                                              |

| DKRZ                   | Deutsches Klimarrechenzentrum, Hamburg, Germany                         |

| DOE                    | Designs of Experiments                                                  |

| DoE                    | Department of Energy                                                    |

| DRAM                   | Dynamic Random Access Memory                                            |

| DVFS                   | Dynamic Voltage and Frequency Scaling i                                 |

| ECC                    | Error Correcting Code                                                   |

| EDF                    | Electricité de France                                                   |

| EDT                    | Event driven tasks                                                      |

| EESI                   | European Exascale Software Initiative                                   |

| EIOW                   | Exascale I/O Workgroup Middleware                                       |

| ESREDA                 | European Safety, REliability and Data Association                       |

| FDL                    | Free Documentation License                                              |

| FEM                    | Finite Element Methods                                                  |

| FeRAM                  | Ferroelectric RAM                                                       |

# D5.1 FIRST INTERMEDIATE REPORT ON CROSS CUTTING ISSUES

| FFT    | Fast Fourier Transform                                                   |

|--------|--------------------------------------------------------------------------|

| FLOPS  | Floating Point Operations per Second                                     |

| FORM   | First Order Reliability Method                                           |

| FW     | Firmware                                                                 |

| GENCI  | Grand Equipement National de Caloul Intensif                             |

| GPU    | Graphics Processing Unit                                                 |

| HDF    | Hierarchical Data Format                                                 |

| HOPSA  | HOlistic Performance System Analysis                                     |

| HPC    | High Performance Computing                                               |

| HW     | Hardware                                                                 |

| IB     | Infiniband                                                               |

| IESP   | International Exascale Software Project                                  |

| INFN   | National Institute of Nuclear Physics, Italy                             |

| INRIA  | Institut National de Recherche en Informatique et en Automatique, France |

| I/O    | Input Output                                                             |

| LANL   | Los Alamos National lab                                                  |

| LARS   | Least-Angle Regression                                                   |

| LGPL   | Lesser General Public License                                            |

| LHC    | Large Hadron Collider                                                    |

| LLR    | Link Layer Retransmission                                                |

| MCA    | Machine Check Architecture                                               |

| MPI    | Message Passing Interface                                                |

| NetCDF | Network Common Data Form                                                 |

| NoE    | Network of Excellence                                                    |

| NTV    | Near-Threshold Voltage                                                   |

| NVDIMM | Non-Volatile Dual In-line Memory Module                                  |

| NVM    | Non-Volatile Memory                                                      |

| NVML   | nVIDIA Management Library                                                |

| NVRAM  | Non-Volatile RAM                                                         |

| OpenCL | Open Computing Language                                                  |

| OS     | Operating System                                                         |

| PAPI   | Performance Application Programming Interface                            |

| PCE    | Parametric Constrain Evaluation                                          |

| PCI-e  | Peripheral Component Interconnect Express                                |

| РСМ    | Phase-Change Material                                                    |

| PCRAM  | Phase-Change RAM                                                         |

| PDE    | Partial Differential Equation                                            |

| RAID   | Redundant Array of Inexpensive Disks                                     |

# D5.1 FIRST INTERMEDIATE REPORT ON CROSS CUTTING ISSUES

| RAM     | Random Access Memory                                    |

|---------|---------------------------------------------------------|

| RAPL    | Running Average Power Limit                             |

| RAS     | Reliability, Availability and Serviceability            |

| RBD     | Random Balance Designs                                  |

| RBM     | Reduced Basis Models                                    |

| ReRAM   | Resistive RAM                                           |

| RMA     | Remote Memory Access                                    |

| R&D     | Research & Development                                  |

| SATA    | Serial Advanced Technology Attachment                   |

| SORM    | Second Order Reliability Method                         |

| SPMD    | Single Program, Multiple Data                           |

| SPEC    | Standard Performance Evaluation Corporation             |

| SQL     | Structured Query Language                               |

| SSD     | Solid State Disk                                        |

| ST-MRAM | Spin-Torque Magnetoresistive RAM                        |

| STTRAM  | Spin Torque-Transfer RAM                                |

| SW      | Software                                                |

| TAU     | Tuning and Analysis Utilities                           |

| ТВВ     | Task Building Blocks                                    |

| тсо     | Total Cost of Ownership                                 |

| TVS     | Through Silicon Via                                     |

| VVUQ    | Verification, Validation and Uncertainty Quantification |

| UQ      | Uncertainty Quantification                              |

|         |                                                         |

# 1. Executive Summary

HPC is a strategic instrument to advance scientific excellence and industry competitiveness. The technological evolution and the increasing computational demand will lead to a new generation of computers composed of millions of heterogeneous cores which will provide extreme performances, in the range of Exascale, in 2020. Such innovative architectures will lead to outstanding technological breakthrough possibilities both in computations and software challenges.

EESI 1 federated the European community and built a preliminary European cartography, vision and roadmap on HPC technology and software challenges.

Now, EESI 2 goes one step further towards implementation, by establishing a structure to gather the European community, by providing periodically cartography, roadmaps and recommendations in defining and following up concrete impacts of R&D projects, detecting disruptive technologies, addressing cross cutting issues and developing gap analysis methodology towards an Exascale roadmap implementation.

This Document reports the first year of activity of EESI 2 WP5 "Cross cutting issues Work Groups". The objective of this WP is to create and manage five working groups (WG) of experts on cross cutting issues for:

- 1) Data management and exploration;

- 2) Uncertainties (UQ/V&V);

- 3) Power & Performance;

- 4) Resilience;

- 5) Disruptive technologies

Cross cutting issues address themes transversal to the different activities from applications to technologies so the activity in WP5 is synergic to the activity in WP3 " Applications" and WP4."Enabling Technologies".

"Cross Cutting issues" is a new WP which was not present in EESI 1, so almost all the topics are new, apart "Resilience" and, in some aspects, "Power and performance".

This Deliverable reports the work done by WP5 in the first year of activity. The five WGs organized the activity with groups of experts, leaders in the specific scientific context of the WG. The activity proceeded first focusing better the state of the art of the topics addressed, then continued to better understand the evolutions in the domains and trying to identify a gap analysis and some recommendations for approaching the Exascale goal. Not all the WGs were able to produce a gap analysis at this stage, as the activity was new, so the gap analysis activity will be better refined in the next reporting period.

The main recommendations identified in the different WGs are reported below, with the intent to advocate actions to prepare European software initiatives for the emergence of exascale computing.

#### - Data management and exploration

Set up actions to address end-to-end techniques for efficient disruptive I/O and data analysis, to describe the full life-cycle of data for a set of applications in order to produce highly parallel data workflows that are consistent all the way from the production to the analysis of the data while considering locality, structures, metadata, right accesses, quality of service, sharing etc.

Promote research in transformational algorithms to address fundamental challenges in extreme concurrency, asynchronous parallel data movement and access patterns, new alternative execution models, supporting asynchronous irregular applications and resilience, to enhance data analytics and computational methods in big data scientific applications.

Promote research in advanced data analytics algorithms and techniques, adopting new disruptive methodologies, to face the analysis of the big data deluge advancing in different scientific disciplines. This research should also promote and support the adoption of efficient metadata specification, management and interoperability in different scientific disciplines, as a key element to govern the scientific discovery process.

#### - Uncertainties (UQ/V&V)

It is important to adopt uncertainty analysis in academic and industrial studies. The use of the uncertainty analysis methodologies requires competence that is somewhat different from the ones required to develop a simulation code, and a key issue is that of training.

Investment is also required in numerical methods. In order to deploy uncertainty analysis on highly CPU-consuming codes, two strategies should be followed: improving adaptive designs of experiments and progressing on surrogate models. Furthermore, traditional uncertainty analysis deals mostly with parameter uncertainty, a huge progress for the validation of scientific codes would be achieved by also taking into account model errors.

The software tools are very important for facilitating the uncertainty analysis dissemination in the numerical simulation community.

Investment on tools and middleware taking into account the problem of resilience to failures is important to make more robust uncertainty tools and therefore to facilitate their wider usage.

Last, modern multiphysics computations involve multiple levels of parallelism (domain decomposition, code coupling, multiscale, etc.). Support developing tools that ensure these different levels of parallelism should be combined with the ones related to the design of experiments for efficient parallelisation of the ensemble.

#### - Power & Performance

Support the development of standard interfaces for power monitoring and power management at all levels of the system architecture. This would need to involve industry and academia. This joined effort will have several outcomes, which could include extensions to performance monitoring standards, such as the Performance Application Programming Interface (PAPI), or the creation of a set of best practices on how to operate systems in an energy efficient manner. This effort should also produce energy efficiency benchmarks to guide and monitor the improvements in energy efficiency.

Define major training and education initiative to prepare developers to face the power wall challenge by applying energy-aware programming techniques. A manual of tips and tricks for green programming would also be an extremely valuable resource for the HPC community.

We need more experts and professional HPC developers to support the wider community with the more efficient use of the expensive Peta and Exascale systems.

Centres of Excellence in performance analysis should be created to help users get acquainted with the available tools, with one-to-one hands-on tutorials provided by tools experts. Ideally these would be based on the users' own codes.

#### - Resilience

Improve checkpoint/restart performance by improving Multi-level checkpoint/restart (by minimizing the overhead of copying checkpoint images between the different storage levels), leveraging application and data properties (like memory access patterns, redundancy across multiple processes data structures) to enhance checkpointing asynchrony.

Improve fault tolerance protocols to increase system efficiency and execution recovery performance in presence of fail stop errors. This requires to understand how message logging can accelerate recovery state inconsistency, how to leverage partial restart to improve system efficiency, how to exploit new MPI concepts like neighbor collectives and RMA. More fundamentally more exploration is needed to refine the notion of global state consistency in the context of HPC executions and take advantage of it.

Investigate alternatives to checkpoint/restart. This covers improving fault tolerance approaches based on task-based programming/execution models, developing new concept of application level process migration, improving replication to reduce its overhead in resources.

Develop a fault aware software stack. This requires that software involved in the resilience (including applications, runtime, OS, etc.) should be fault aware and a notification/coordination infrastructure should guarantee relevant and consistent notifications/decisions/actions between these software layers.

Improve failure prediction and proactive actions. There are essentially two main research problems: 1) increase significantly the number of correctly predicted failures and 2) design failure prediction workflow to work with extremely large and growing system data sets (>1GB per day).

Improve resilient algorithms for fail stop errors and data corruption and their integration in the global resilience design. In particular the composability of resilience algorithms with other fault tolerance solutions should be explored.

#### - Disruptive technologies

Concerning the roadmap to exascale, the following recommendations are suggested to easily take-up disruptive technologies that may become available.

Recommendations related to the I/O and Memory disruption:

- a) analyse alternatives to parallel Filesystems, improve and revise them, together with their usage model;

- b) rewrite applications I/O functionalities to work at an higher level (Data container);

- c) promote tiered memory and I/O systems;

- d) re-write application to improve data locality.

Recommendations related to Cooling technologies and Facility management:

- a) evaluate and implement energy aware monitoring systems (better if embedded in the operating system), schedulers and applications;

- b) search for opportunities of joint venture with energy company, or heat re-use.

Recommendations concerning the Network infrastructure:

- a) develop networking system with the possibility to implement an adaptive topology, to enhance the routing capability (useful to avoid message congestion and fault tolerance)

- b) develop active network chip that can perform some data processing "on the fly" (data conversion, compression, elemental arithmetic operation);

- c) tests and validate direct end-to-end data exchange technology.

Recommendations concerning Data Transfer technologies

- a) promote early adoption of photonic technology;

- b) find synergy between HPC and BigData workload.

Recommendations concerning Semiconductor technology:

- a) study and evaluate fine grain resource management to mitigate extreme parallelism;

- b) investigate and promote new parallel paradigms dataflow inspired, leading to tiny "codelets" that can be more easily scheduled, dispatched and placed close to the data (to avoid data movement);

- c) develop intelligent scheduling functionalities to move execution threads close to the data.

# 2. List of Experts and Work Methodology

The objective of WP5, leaded by Giovanni Erbacci (CINECA) is to create and manage five working groups of experts on cross cutting issues:

- WG5.1 Data management and exploration (chair: Francois Bodin, CAPS) ;

- WG5.2 Uncertainties (UQ/V&V) (chair: Vincent Bergeaud, CEA);

- WG5.3 Power & Performance (chair: Simon McIntosh-Smith, Bristol University);

- WG5.4 Resilience (chair: Franck Cappello, INRIA);

- WG5.5 Disruptive Technologies (chair: Carlo Cavazzoni, CINECA).

After the EESI-2 Kick-off meeting, held in Paris on 18 September 2012, the activity in WP5 started soon. All the chairs and vice provided a more accurate definition of their WGs, a methodology for the work activity and started the enrolment of the experts for each of the five WGs.

Regular monthly teleconfereces have been organised by the WP5 chair with the chairs and vice chairs of the five WGs to better co-ordinate the whole activity in WP5. The relevant material has been uploaded in the EESI internal web site.

All the WP5 chairs and vice chairs attended the first annual EESI conference organised on May 28 and 29 2013 in Le Tremblay near Paris. The meeting was the occasion to present the first activity in each WG and discuss and refine better the activity with the participants of the other WPs and some external experts.

A total of 43 expert have been enrolled in the 5 WGs of WP5, during the first year of activity. As presented in Figure 1, the experts represent 9 different Countries, including Japan and US, coming from Academia, Research Institutions and Industries.

Figure 1: WP5 Experts distributed per Country (43 Experts from 9 Countries)

In the following, the list of the external experts and a brief description of the activity organisation is provided for each WG.

# 2.1 WG 5.1 Data Management and Exploration

WG 5.1 is chaired by Francois Bodin, a founder and the CTO of the French CAPS-Enterprise Company.

The following experts have been appointed to contribute to the WG:

# D5.1 FIRST INTERMEDIATE REPORT ON CROSS CUTTING ISSUES

- Jean-Michel Alimi, Observatoire de Paris, Meudon, France

- Gabriel Antoniu, INRIA, France

- Georges Hebrail, EDF, France

- Jacques-Charles Lafoucrière, CEA, France

- Malcolm Muggeridge, Xyratec, UK

- Kenji Ono, Riken, Japan

- Stéphane Requena, GENCI, France

- Alex Szalay, Johns Hopkins University, US

- Jean-Pierre Vilotte, Institut de Physique du Globe de Paris, France.

Once enrolled the external experts, the chair distributed a preliminary position document and a plan of the work. Then the WG5.1 activity proceeded in a electronic way by email communication and periodic teleconferences. Recently, the meeting in Le Tremblay was the occasion to refine the first results and the main recommendations for the data management and exploration topics.

# 2.2 WG 5.2 Uncertainties (UQ/V&V)

WG 5.2 is chaired by Vincent Bergeaud, Chef de laboratoire Génie Logiciel at CEA in France, and cochaired by Alberto Pasanisi (EDF, France).

The following experts are contributing to the workgroup:

- Stefano Tarantola, JRC-ISPRA, Italy

- Christophe Prud'homme, University of Strasbourg, France

- Olivier Le Maître, LIMSI, Duke University, US

- Renaud Barate, EDF R&D, France

- Bertrand looss, EDF R&D, France

- Fabrice Gaudier, CEA, France

Once defined the list of the experts, WG5.2, organized a first workshop to investigate the topics of HPC and uncertainties. The workshop was organized in Paris on April 22 and 23, 2013. During the first day the presentations focused on numerical methods instead, on the second day, the software aspects were investigated. The agenda is reported the Table 1 below.

| Workshop on HPC and Uncertainties - Paris, 22-23 April 2013<br>April 22 HPC and Uncertainties: Numerical methods |                                                                                                        |                                          |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------|

| 9h30                                                                                                             | Welcome                                                                                                |                                          |

| 10h                                                                                                              | Introduction EESI2 WG 5.2                                                                              | V. Bergeaud - A. Pasanisi                |

| 11h                                                                                                              | Gaussian processes in uncertainty analysis                                                             | B. looss (EDF R&D)                       |

| 12h                                                                                                              | Lunch                                                                                                  |                                          |

| 14h                                                                                                              | Reduced basis methods and high performance computing: applications to non-linear multiphysics problems | C. Prud'homme<br>(Univ. Strasbourg)      |

| 14h50                                                                                                            | Spectral methods for Uncertainty Quantification                                                        | O. Le Maître (Duke University,<br>LIMSI) |

| 15h40                                                                                                            | Break                                                                                                  |                                          |

| 16h                                                                                                              | Sensitivity analysis                                                                                   | S. Tarantola (JRC ISPRA)                 |

| 16h50                                                                                                            | Wrap up                                                                                                |                                          |

| 17h                                                                                                              | adjourn                                                                                                |                                          |

|       | April 23 HPC and Uncertainties: Softwa                         | are aspects                    |

|-------|----------------------------------------------------------------|--------------------------------|

| 9h    | Design of experiments with the URANIE platform                 | V. Bergeaud, F.Gaudier (CEA)   |

| 9h50  | Deployment of Design Of Experiments with<br>OpenTurns software | R. Barate (EDF R&D)            |

| 10h40 | Break                                                          |                                |

| 11h   | Applicative needs                                              | A. Doering (Oxford University) |

| 11h30 | Work plan and conclusion                                       | V. Bergeaud - A. Pasanisi      |

| 12h30 | Adjourn                                                        |                                |

Table 1: Agenda of the Workshop on HPC and Uncertainties, Paris, 22-23 April 2013

The slides that were presented during the workshop are available on the EESI website: <a href="http://www.eesi-project.eu/pages/menu/eesi-access.php?g=88">http://www.eesi-project.eu/pages/menu/eesi-access.php?g=88</a>

The workshop was the occasion for better investigate the different topics of uncertainties and allowed to define a set of recommendations for exascale.

# 2.3 WG 5.3 Power & Performance

WG 5.3 is chaired by Simon McIntosh-Smith, head of the Microelectronics Research Group in the Department of Computer Science at the University of Bristol (UK). Thomas Ludwig ), computer scientist at the Climate Computing Centre University Hamburg (DKRZ, Germany) is the co chair; WG5.3 in the first year of activity, appointed five experts in the different fields of micro electronics, computer architectures, energy efficiency, computer applications and performance:

- Alex Ramirez, Barcelona Supercomputing Centre, Spain;

- Matthias Müller, RWTH Aachen University, Germany;

- Jean-Marc Pierson, Laboratoire IRIT, Université Paul Sabatier, Toulouse, France;

- Laurent Lefevre, INRIA / University of Lyon, France;

- James Perry, EPCC, University of Edinburgh, UK.

The WG5.3 technical experts have held a number of conference calls to establish the scope of this working group. The interactions culminated in a face to face meeting organised to coincide with International SuperComputing (ISC) in Leipzig, Germany in June 2013. The majority of the technical information in this report was gathered from a pro-forma circulated amongst the experts at the end of this process, just after ISC. A final conference call was used to discuss the findings.

# 2.4 WG 5.4 Resilience

WG 5.4 is chaired by Franck Cappello, senior researcher at INRIA and Project Manager of Research on Resilience at the Extreme Scale at Argonne (US). WG 5.4 appointed at the beginning seven experts in resilience

- Luc Giraud, INRIA, France;

- Torsten Hoefler , ETH Zurich, Switzerland;

- Simon McIntosh-Smith, Bristol University, UK ;

- Christine Morin, INRIA, France;

- Bogdan Nicolae, IBM Research Lab, Dublin, Ireland;

- Pascale Rosse-laurent, BULL, France;

- Osman Unsal, Barcelona Supercomputing Centre, Spain;

After the engagement of the experts, the activity in the WG proceeded with the analysis of existing reports and the material produced in EESI 1. A WIKI has been set up for the WG members at

<u>https://collab.mcs.anl.gov/display/ESR/EESI2+Resilience+Working+Group</u> to share the documents and the analysis.

The experts worked electronically and different teleconferences have been organized to produce a gap analysis between existing reports and projection about the resilience challenge for exascale simulation. In addition, a set of recommendations based on this gap analysis have been produced. Since the EESI 2 project is in its first year and since the work of the WG started recently, the recommendations may differ from the ones that will be emitted by the WG at the end of the project.

# 2.5 WG 5.5 Disruptive Technologies

WG5.5 is chaired by Carlo Cavazzoni, head of the HPC Production Services Division at the CINECA supercomputing centre in Italy and co-chaired by Marie-Christine Sawley, Director of the Intel Exascale Lab in Paris. Facing exascale, disruptive technologies address challenge aspects in different fields like Semiconductor Technology, Packaging, Data transfer, Memory, Network, Cooling and Infrastructure, I/O Subsystem. To address the above issues the following main experts have been initially engaged:

- Shekhar Borkar, Director of the Intel Extreme-scale Technologies Lab, US

- Bruno Michel, IBM Research Laboratory, Zurich, Switzerland

- Patrick Demichel, HP, Lyon, France

- Piero Vicini, INFN National Institute of Nuclear Physics, Rome, Italy

- Giampietro Tecchiolli, Eurotech, Italy

- Malcolm Muggeridge, Xyratex, UK

As a first action of this WG, the expert have been interviewed by phone and they have been requested to send papers and reference of their activity on disruptive technologies, The material produced has served as the basis to prepare a WG workshop. The workshop took place in Milan, Italy on April the 15, 2013. The agenda of the workshop is reported in **Table 2**. The workshop was the occasion to better analyze and investigate the disruptive technologies in different fields and produce some initial roadmaps and recommendations.

Further experts will be engaged in the next period to address specific issues related to disruptive technologies.

|       | EESI2 WG5.5 Disruptive Technologies Workshop<br>Milan (Italy) April 15th, 2013     |

|-------|------------------------------------------------------------------------------------|

| 11:00 | Introduction. Carlo Cavazzoni (CINECA) Marie-Christine Sawley (Intel)              |

| 11:30 | Cooling and engineering: high efficiency solutions Giampiero Tecchiolli (Eurotech) |

| 12:15 | Lunch                                                                              |

| 13:30 | I/O Technologies Malcolm Muggeridge (Xyratech)                                     |

| 14:15 | Packaging and microfluidics Bruno Michel (IBM)                                     |

| 15:00 | Silicon photonics Patrick Demichel (HP)                                            |

| 15:45 | Coffee break                                                                       |

| 16:00 | Semiconductor Technology: Near threshold voltage Shekar Burkhar (Intel)            |

| 16:45 | Network technology: Adaptive free devices Piero Vicini (INFN)                      |

| 17:30 | Discussion on possible recommendations                                             |

| 18:30 | Wrap-up                                                                            |

Table 2: Agenda of the Workshop on Disruptive Technoloogies, Milan, 15 April 2013

# 3. WG 5.1 Data Management and Exploration

# 3.1 Introduction

This section proposes R&D actions/initiative on one of the major challenge of exascale applications: Data management. On the new generation HPC systems, the memory by core will decrease dramatically and at the same time data to be treated will increase dramatically too [1] [2] [3]. The recommendations aim at ensuring a coherent approach toward the evolution on management of I/O, such as big data transfer, storage, compression, massively parallel I/O, memory access, memory storage, etc.

Previous European Exascale Software Initiatives [4], [5], have explored the data issues from the technological point of views. For instance they identified critical topics such as "parallel file systems, disaster recovery mechanisms, mechanisms for end-to-end data integrity, data mining and visualization tools, data reduction techniques to carry out in-situ domain-specific data reduction and feature extraction, etc."

Workgroup 5.1 has been addressing "Data management and exploration" in Exascale applications viewed as the organization of the scientific discovery workflow. This is illustrated in Figure 2. In this figure, data may follow any paths (blue arrows) in the ecosystem, each component having its own performance profile, quality of service and cost. For instance while HPC technology optimizes writing in parallel the data, data mining techniques favour reading. Choosing to use one or the other technology must be carefully planned according to a global view of the workflow.

Figure 2: Complex work flow of Exascale applications

One important consideration in this work is the rising price of IO systems on one hand. On the other hand, as a deluge of data is to be expected, synergies between big data and traditional HPC techniques have to be well thought-out. Data types are also an important concern. For instance, data from sensors cannot be regenerated and must be stored safely while some data produced by simulation may be easier to re-compute when combine with in-situ data processing technique. Each data must be stored and organized to use the proper resources. As well metadata must be kept consistent all the way. This likely will strongly disrupt current practices.

In a nutshell, data management and I/O performance will strongly influence for the design of applications. However this topic cannot be viewed only under the technology angle. Indeed, designing the applications requires finding tradeoffs between in-situ vs. ex-situ processing, selecting data format, access policy, data relocation, format changes, etc. These tradeoffs are not only driven by technology

and performance but also by the ecosystem exposed to the researchers. Furthermore, It is important to note that a global efficient use of the exascale resources can be contradictory with the objectives of individual research teams. Understanding the full cycle of data is probably the most important question to drive exascale technology development.

# 3.2 Challenges

When addressing end-to-end data life cycle many challenges arise due to combining the technology, the human resources and the ecosystem economy.

Designing an exascale applications that make rational and efficient uses of communication, compute, storage resources requires engineer skills that are currently in shortage or just not available to scientists. New best practices will have to be defined and implemented. They will very likely require setting up interdisciplinary support team capable of addressing extreme parallelism, fault tolerance and IO issues.

Because of the expected deluge of data, new data analysis techniques must be designed. Big data technology may provide new disruptive methods for such task. These techniques need to be extended to take advantage of highly scalable parallel infrastructure. This may be a return contribution of HPC to the big data field. Behind this topic lies many complex and holistic issues such as: serialization/deserialization of data, design of data structures able to cope with highly asynchronous execution as well as compute / IO activities interleaving. More generally, data mining techniques must be established between HPC and big data usual formats.

Metadata management and specification is a critical challenge. They are keys elements in the science discovery process. Their design is particularly important to obtain a consistent end-to-end use of the data. Furthermore, they impact on sharing policy management implementation (e.g. at the core of the decision process concerning data to be set public, what storage migration, etc.).

Analysis and visualization of data produced by large-scale simulations are often sidelined in favour of pure computation performance. As we foresee exascale systems in the next decade, the offline analysis approach shows its limits: more and more scientists see the scalability of their simulations dropping because of unmatched computation and I/O performance as well as higher I/O variability. However, in-situ approaches (potentially more efficient) have difficulties in getting accepted, as scientists fear to dive into fundamental code changes in a simulation they have used for years. Defining the right trade-off here is a challenge. Also related to the same limitation in I/O performance, HPC scientists predict fundamental changes in the way I/O and data management will be handled in the near future. In particular, the heterogeneous processor environment and memory hierarchy of the new platforms, together with the increasing use of GPU and accelerators, open new alternatives for data analysis.

Maybe the biggest challenge of all, is to provide scientists with an ecosystem that is stable, intelligible and efficient. The exascale technology is very likely to have many handling hard constraints and a high operational cost (e.g. energy). Missing to understand the full consequences of technical choice on the complete workflow is likely to produce expensive use of resources and high probably of application development failure.

# 3.3 Impact on application development

This paragraph explores the potential data management issue and exploration impact on applications implementation and design.

A first trade-off to deal with is concept of "what data to output?". For instance, it is frequent that adding more in-situ computation will negatively impact the efficiency of the simulation part of the applications. However, if this later provides for a faster and simpler analysis of the data, it will be worthwhile to pay the corresponding penalty. It is important to remember that human time, even in exascale environment remains the most expensive resources.

The data life cycle must be clearly understood to allow building an indexing and typology of the data that promote an efficient use of the different storage systems. The most reliable storage must only be

used in a cost-effective manner. For instance, it is necessary to distinguish the needs in pre- and postprocessing so that the right technology could be used. Typically, three cases can be distinguished:

- 1) Post processing very large, out of memory data that requires powerful computing power (e.g. out of memory FFTs);

- 2) In-memory processing of mid-size chunk of data (e.g. can benefit of Hadoop technology);

- 3) Complex search with associative patterns over very large, out of memory data.

These techniques, to be fully exploited in an HPC context, will require disruptive practices.

Applications must allow optimizing the use of IO bandwidth thanks to interleaving compute and data transfers in a manner known/understood by the system. Indeed, contrary to computing resources, an application uses IO only at some execution point; this idle IO time can be exploited by another applications in order to make an efficient use of the IO sub-systems.

When designing the simulation, all numerical model trade-offs must be considered in order to minimize fault-tolerance needs, in/out-situ analysis, etc. For instance, it is probably better considering multiple middle scale simulation to build the full picture rather than a large atomic one. The right trade-off is in the end dictated by the "economy" of the exascale system.

As a consequence of the previous considerations, system and programming environment designers should provide to application developers efficient and standard APIs (or other methods), and corresponding best practices, to drive the hierarchies of storage to use and to describe more about the exploitation of the data.

# 3.4 Findings

Here is a summary of the findings of WG 5.1. These findings are consequence of the impact of data management and exploration in a complete workflow of an exascale application:

- 1) Both HPC and Database communities need to connect to design the technology and corresponding best practices;

- 2) There is a need for describing the technology deployment scenarios and the available options for organizing the data storage and processing flow. This aims at allowing system designers to understand off-line analysis, in-situ analysis, hybrid schemes, etc. The outcomes of these scenarios will be to identify big data technology and HPC technology synergies, identify workflow time-consuming / costly parts for a given application domain, to help to carefully examine the candidates of exascale computing platforms;

- Exascale technology should also be available as many peta-scale systems in order to allow an adaptation of the computing and storage strategy according to the scientific objectives. Furthermore smaller size machine may be very convenient for data post-processing;

- 4) Data storage management must be flexible enough to accommodate use change of data (i.e. locality optimization);

- 5) Exascale technology is asking for new support people with technical profile that can bridge the gap between the "data-I/O" technology and the applications / scientific discovery process. There is a strong need in training of engineers in I/O systems.

Overall, this translates into the need to build an ecosystem were computing, storage, network resources uses/deployments (and corresponding business model) are carefully planned and stable overtime to allow an efficient local (e.g. scientist view) and global (e.g. computing centre operators) utilization. Support engineering teams, able to provide insights to scientists from the design phase to the implementation phase of the applications, will be a key component of this ecosystem.

# 3.5 Recommendations

The main recommendation of WG 5.1 is to set up actions to address "**End-to-end techniques for efficient I/O and data analysis**" to describe the full life-cycle of data for a set of applications in order to produce designs/workflows that are consistent all the way from the production to the analysis of the data while considering locality, structures, metadata, right accesses, quality of service, sharing etc. This action can encompass the following items:

- Support research in transformational algorithms to address fundamental challenges in extreme concurrency at the benefit of data analytics and computational methods for data intensive applications;

- Support highly parallel data workflow, encompassing I/O middleware and scientific data formats supporting high-level data objects and data access patterns, scientific database technologies and indexing methods;

- Push research in advanced data analytics algorithms and techniques to face the analysis of big data in different scientific applications;

- Support the adoption of efficient metadata specification, management and interoperability in different scientific disciplines;

- Specification scenarios for technology deployment and the available options for organizing the data storage and processing flow;

- Gathering Big data and HPC experts to identify best practices to be convey;

- Specifying curriculum for support engineering teams;

- Development of mini-apps to help conducting research in IO and data managements.

If these recommendations are implemented we expect the following outcomes:

- 1) Better designed applications and ability to innovate by cross fertilization of HPC and Bid Data technology;

- Best practices to be available to scientist and support teams (for instance via a Massive Open Online Course);

- 3) Coherent policy for managing exascale resources;

- 4) Evaluation of exascale platforms in regards of the full operational chain;

- 5) Afford the analysis challenges posed by the big data deluge in different scientific domains.

# 4. WG 5.2 Uncertainties (UQ / V&V)

# 4.1 Introduction

Computer simulation is undoubtedly a fundamental question in modern science and engineering. Whatever is the purpose of the study, computer models help the analysts to forecast the behavior of the system under investigation in conditions which cannot be reproduced in physical experiments (e.g. accidental scenarios), or when physical experiments are theoretically possible but at a very high cost.

The need for simulating and forecasting gave indeed a dramatic momentum in the last decades to the growth of computers' power and vice versa. Since the very first large scale numerical experiments carried out in the 40's, the development of computers (and computer science) has gone pair-wise with the will of simulating more and more deeply, more and more precisely, physical, industrial, biological, economic systems.

A deep change in science and engineering has gone on in the last decades in which the role of the computer has been compared to the one of the steam engine in the first industrial revolution [22]. Together with formulating theories and carrying physical experiments, computer simulation has rapidly become a *third way to Science* [23] which allows solving problems which were absolutely unaffordable in a not so far past.

We believe in computer simulation as a major tool in daily engineers' work; simulation is a great tool for understanding, for forecasting, for guiding decision. We think that the possibility to simulate more and more complex phenomena, taking into account the effect of more and more input parameters must be seen as a chance, but, at the same time, we are aware of the fact that quantitative uncertainty assessment of results is a fundamental issue for assuring the credibility of computer model based studies, and represents a challenge too.

Besides technical and theoretical difficulties, maybe the most challenging point is, in industrial practice, to bridge the cultural gap between a traditional engineering deterministic viewpoint and the probabilistic and statistical approach which consider the result of a model as an "uncertain" variable.

Even if the fundamentals of these topics are rooted since decades in probabilistic and statistic literature, in the last years there has been a considerable rise of interest in industries and academia in the uncertainty quantification (UQ) of computer models' results.

A quick look at the recent bibliography can witness the variety of disciplinary fields involved: e.g. nuclear waste disposal, water quality modeling, avalanches forecasting, welding simulation, buildings performance simulation, galaxies formation, climate modeling, fires simulation etc.

In the last decade, in the frame of an ESREDA (European Safety, REliability and Data Association) project, CEA and EDF R&D settled a global methodology of uncertainty treatment that has been now accepted and improved by industrial and research institutions. As currently deployed in the industrial practice of engineering, the methodology essentially focuses on the so-called *parametric uncertainties*, i.e. the ones affecting the input parameters of a model, whatever it is: a complex numerical code which requires an approximated resolution or an analytical expression. It does not question explicitly uncertainties attached to the computer model itself, coming from the necessarily simplified modeling of the physical phenomenon under investigation, nor numerical uncertainties due to its practical implementation into a computer code.

The step forward is to develop and to spread in the engineering community an enhanced unified framework for model verification & validation and uncertainty quantification, what is commonly called *VVUQ*. This unified framework shall need at the same time:

- multidisciplinary skilled teams (statistics & probability, numerical analysis, PDE, physicians),

- high computational power, as the statistical methods for calibration and validation need to evaluate several times a (possibly) costly numerical code.

HPC and uncertainty quantification have a two-sided relationship. On the one hand, the ever increasing size of the computational data leads to increasing sources of uncertainties, due to the accumulation of numerical errors. On the other hand, HPC gives access to computational power that can be used to tackle explicitly the evaluation of uncertainties, be it by embedded methods or by design of experiments. The activity in WG 5.2, as reported in this section, aimed at exploring these different aspects of the relationship between uncertainties and HPC. We will identify methodologies for

the analysis of these uncertainty sources, software tools related to uncertainty analysis and give guidelines for the evolutions required both in tools and in methodologies for exploitation of Exaflop machines.

# 4.2 Characterization of Uncertainty and Terminology

The uncertainties in the numerical simulation process can arise from different sources:

- Lack of knowledge on a physical parameter (epistemic uncertainty)

- Parameter with a random nature (aleatory uncertainty)

- Uncertainty related to the model (model error)

- Uncertainty related to the numerical errors (numerical errors).

Taking into account these uncertainties is essential for the acceptance of numerical simulation for decision making. These uncertainties must be integrated in the verification and validation process of the simulation codes. This process is now commonly called VVUQ (Verification, Validation and Uncertainty Quantification). Verification consists in checking that the equations underlying the code is correctly solved. Validation is the stage during which the predictive capability of the numerical model is checked against experimental data or a reference model [24],[25].

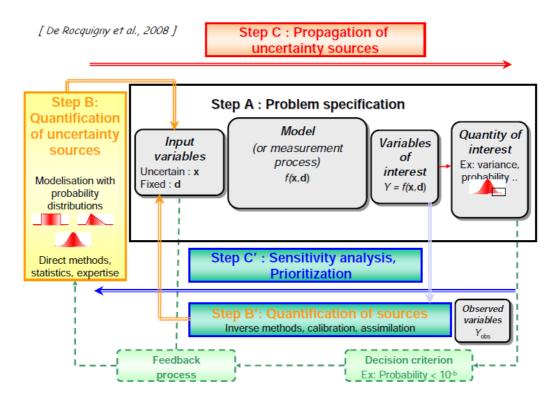

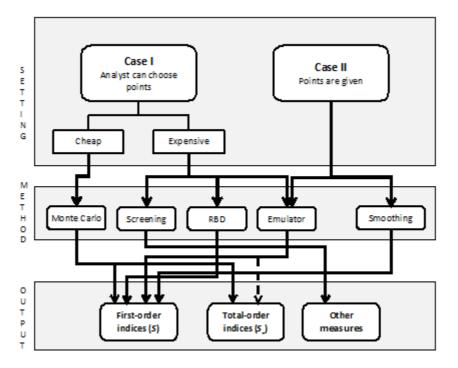

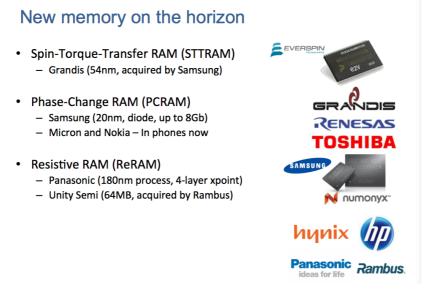

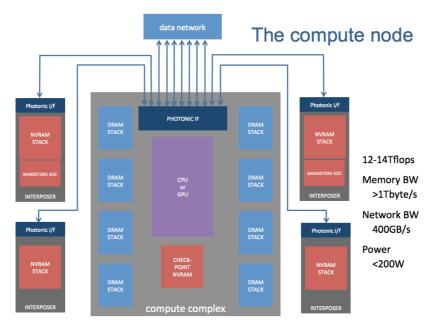

# 4.3 Embedded uncertainty analysis methods